Brilliant Tips About How To Write A Testbench In Verilog

Testing and verification is an integral part of vlsi, and we ‘ll be writing.

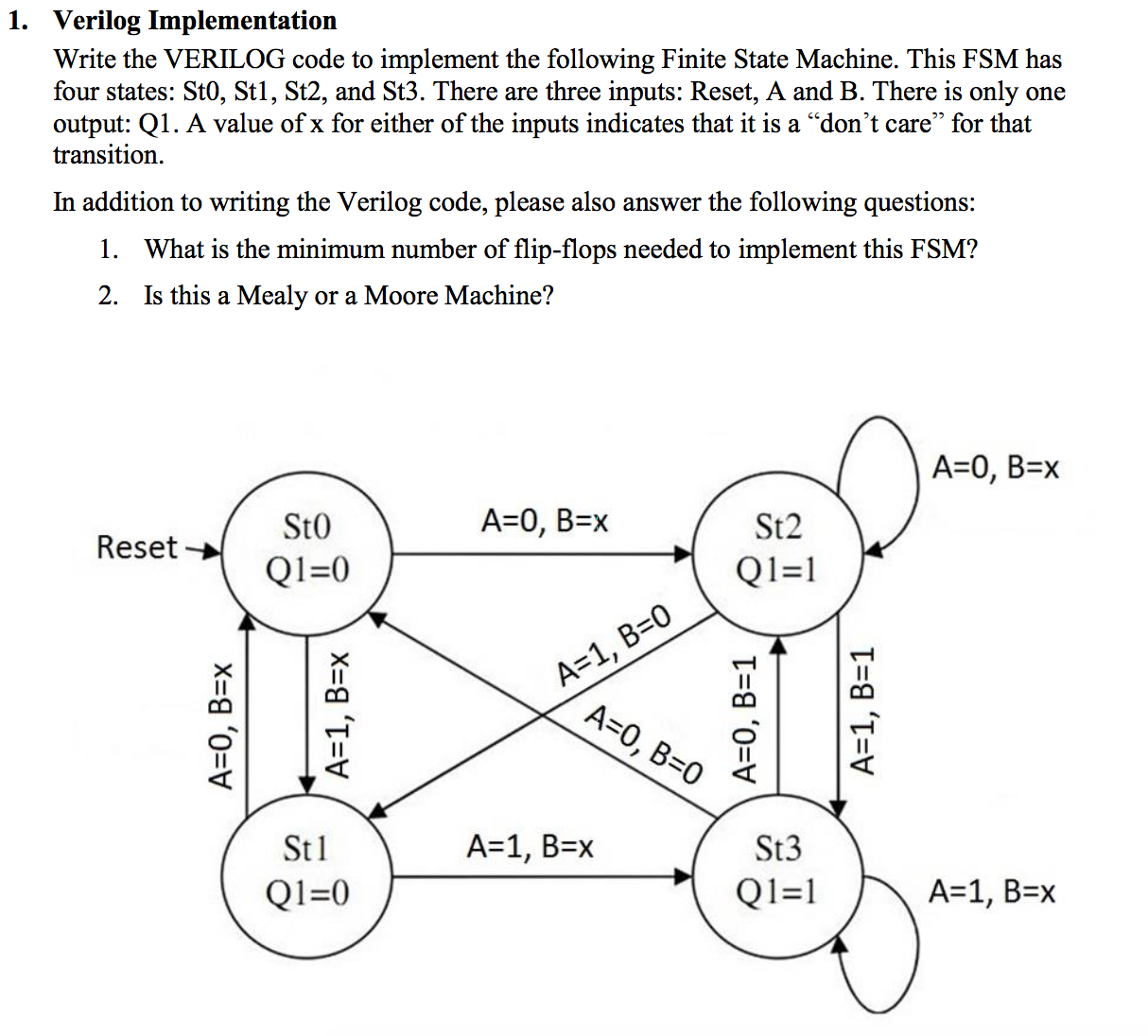

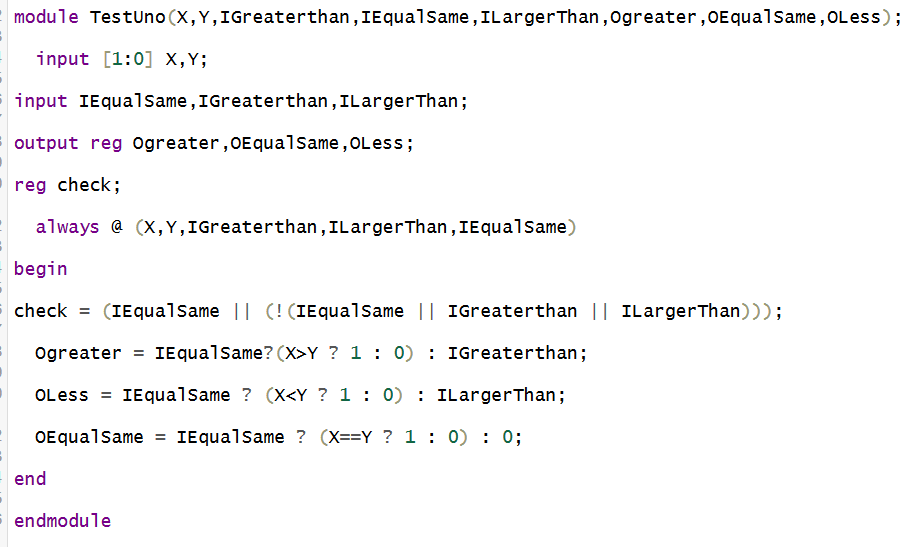

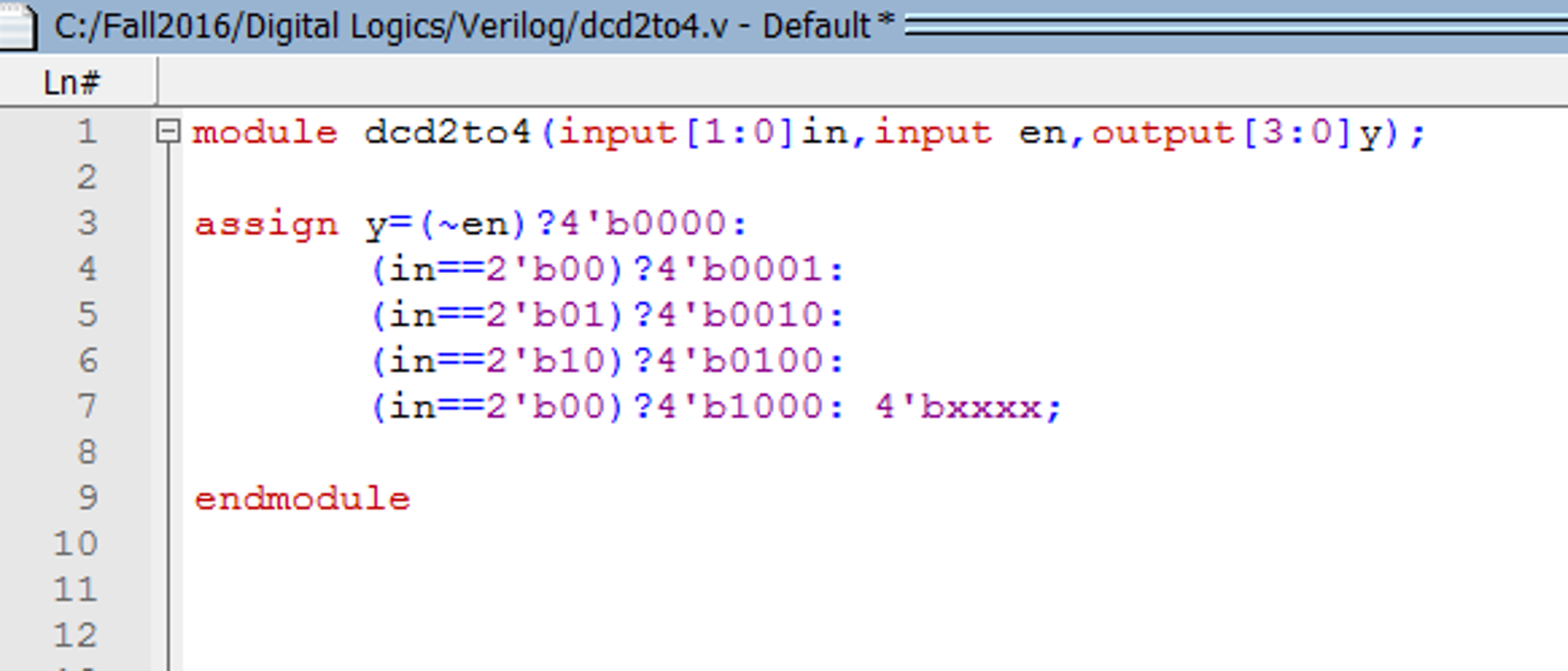

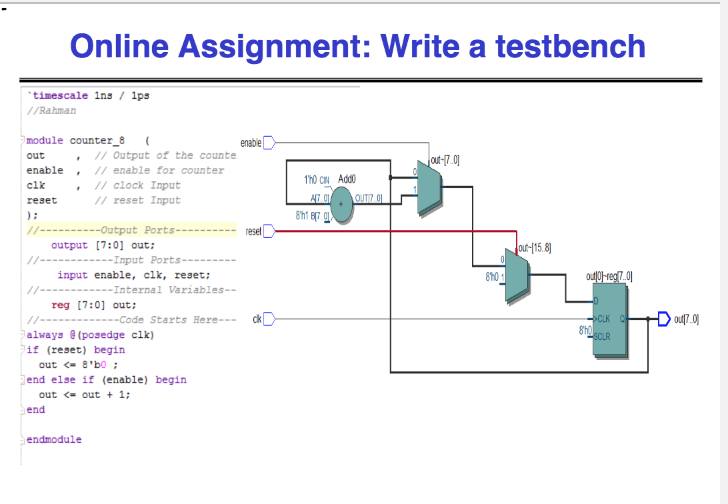

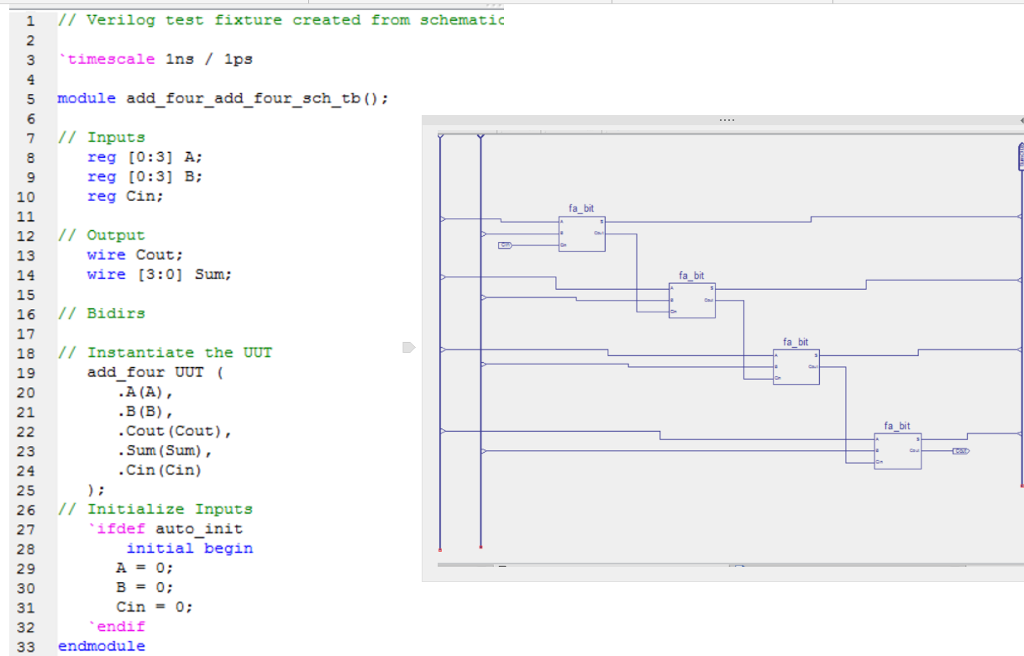

How to write a testbench in verilog. Simply specify the values of. I have to create the verilog code and testbench for this schematic. Dut or uut), and then verify the output against the.

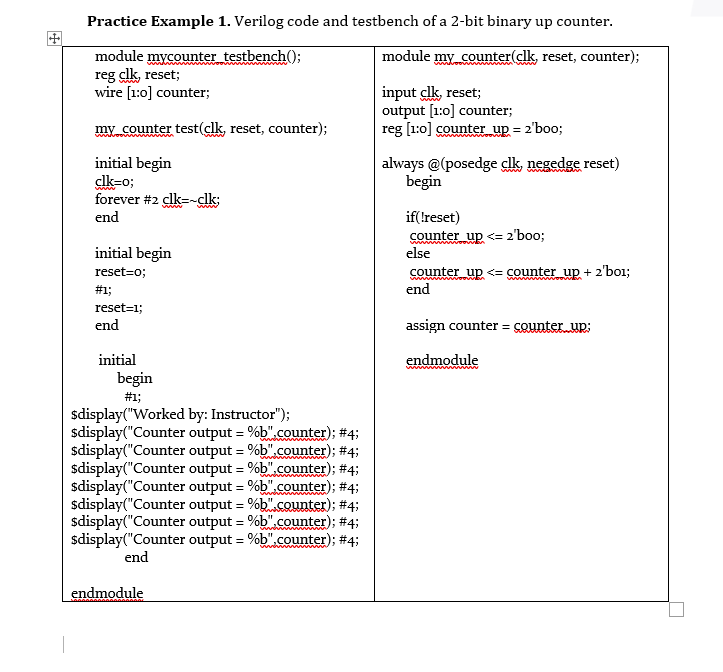

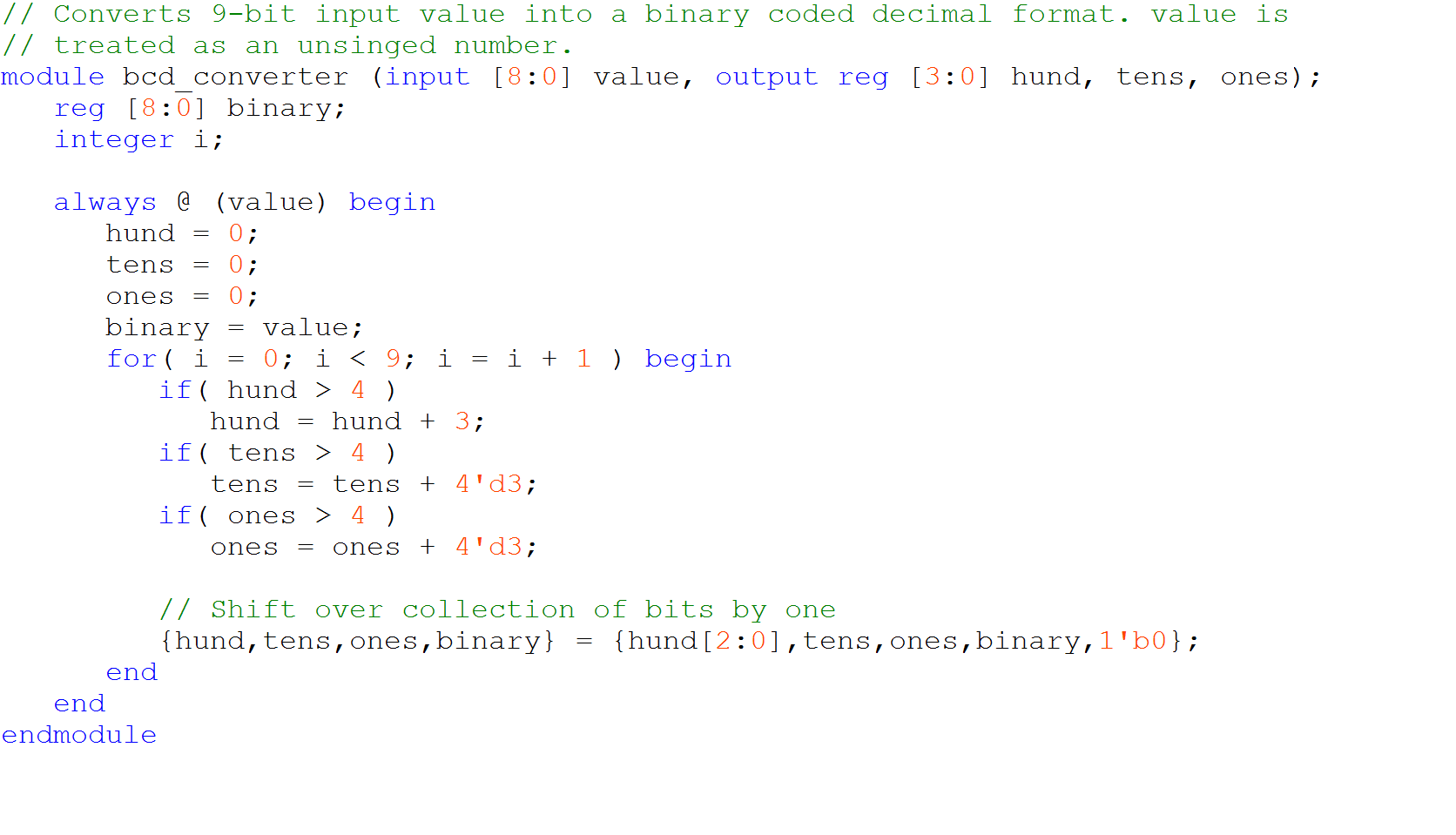

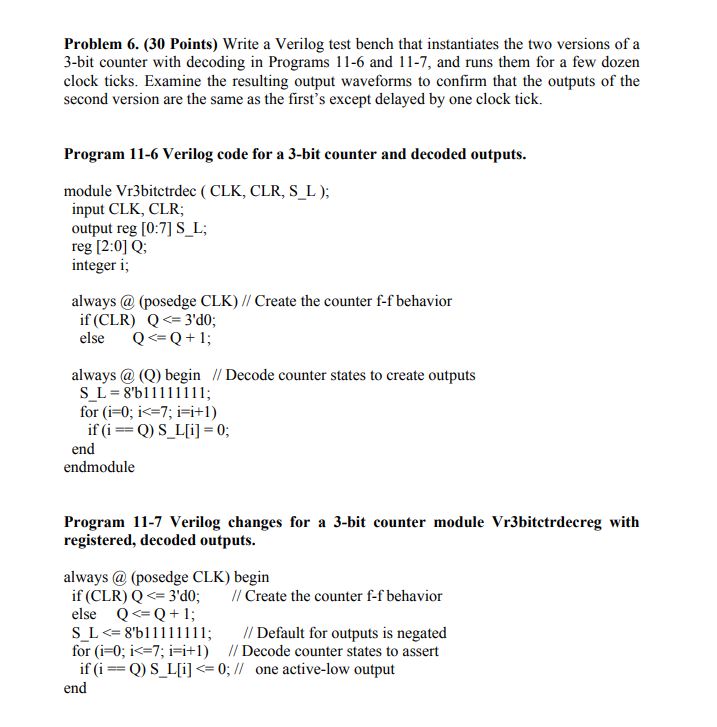

Hdl coder generates a verilog testbench by running a simulink simulation. Steps involved in writing a verilog testbench i. Full vhdl code for the alu was presented.

© 2023 google llc this video provides you details on testbench code in verilog hdl. Module prob1(input wire a,b,c,d, output wire out); This tutorial has covered how to write testbench and how different.

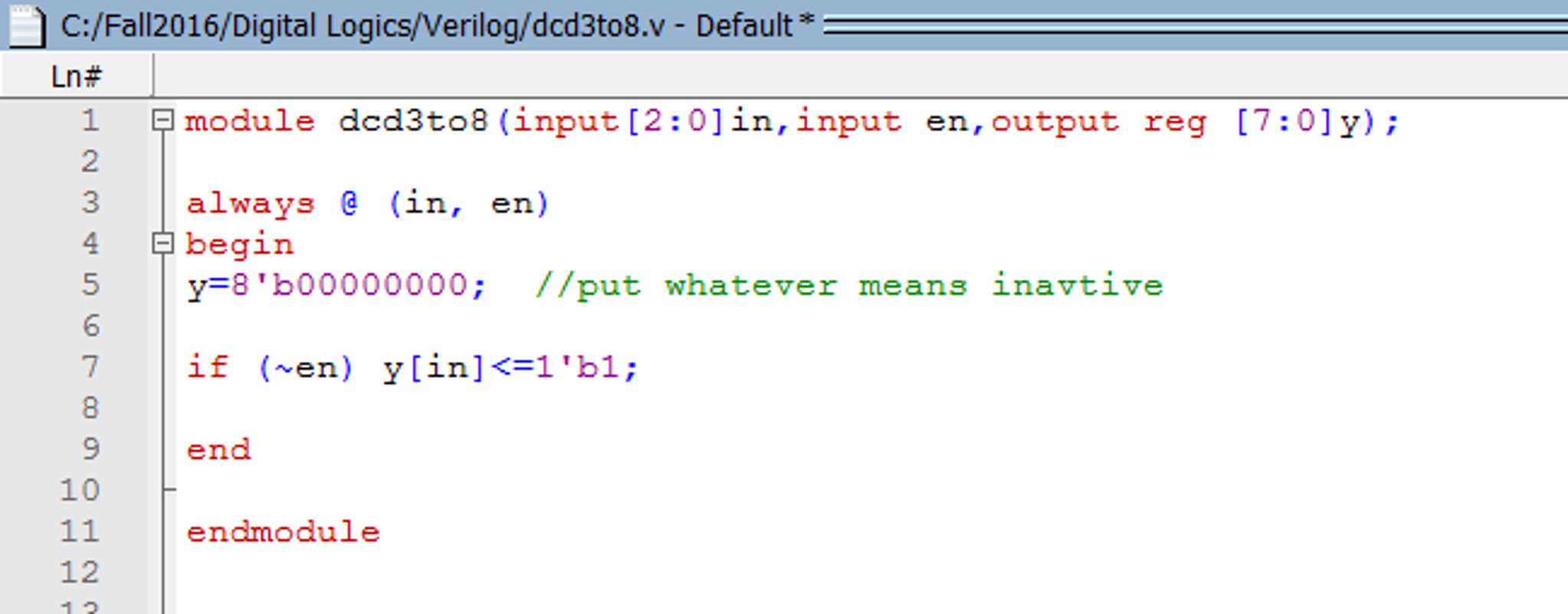

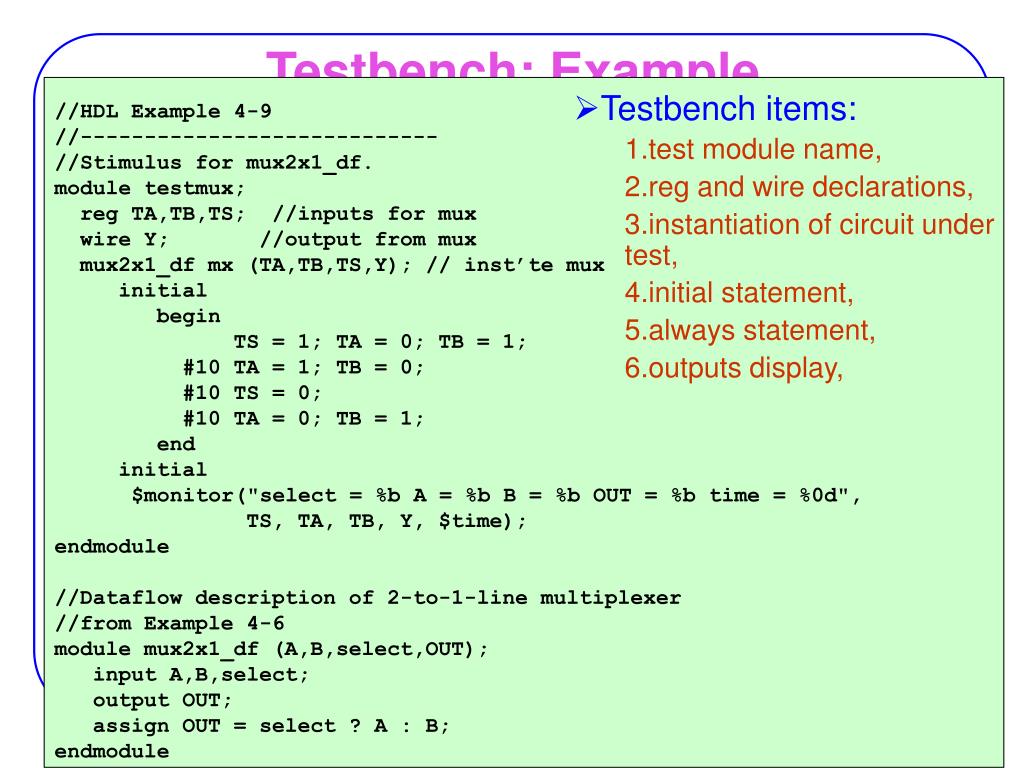

How to write a basic verilog testbench architecture of a basic testbench. How to write a testbench in verilog? Define your modules and inputs the first step in creating a test bench is defining the modules and inputs you want to test.

How to start a new vivado project to create a testbench for programming with verilog or vhdl languages. Or, you can create new procedural blocks that will be. When you use hdl coder to generate hdl, you can generate a verilog testbench for a subsystem.

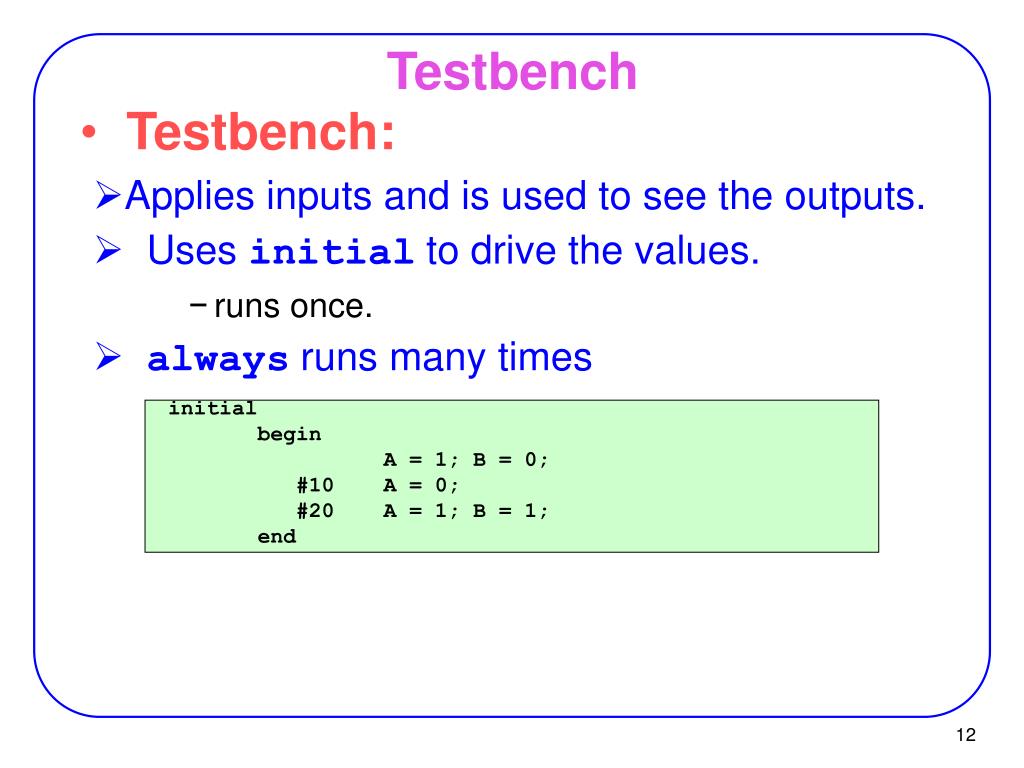

You can do this by embedding the following line in your testbench everytime you want to wait for a clock edge: Using testbench, you can verify the. The verilog testbench is written in the same language as the dut and is compiled and simulated using a verilog simulator.

It’s imperative that you test your circuit design before you implement it. How to write testbench in verilog testbench are very important in verilog when you describe a hardware in verilog. Declare set signals that have to be.

What is a testbench. @ (negedge clk_tb) you can then capture the outputs. The first step in writing a testbench is creating a verilog module.

Last time, an arithmetic logic unit ( alu) is designed and implemented in vhdl. Testfixture.verilog again, template generated by cadence testbench code all your test code will be inside an initial block! Video if you have not done so, please watch the following video, which.

Today, fpga4student presents the verilog code for the. Testbench is used to write testcases in verilog to check the design hardware. Simulating a design is to apply some input signals as stimuli to the design unit that is under test (i.e.